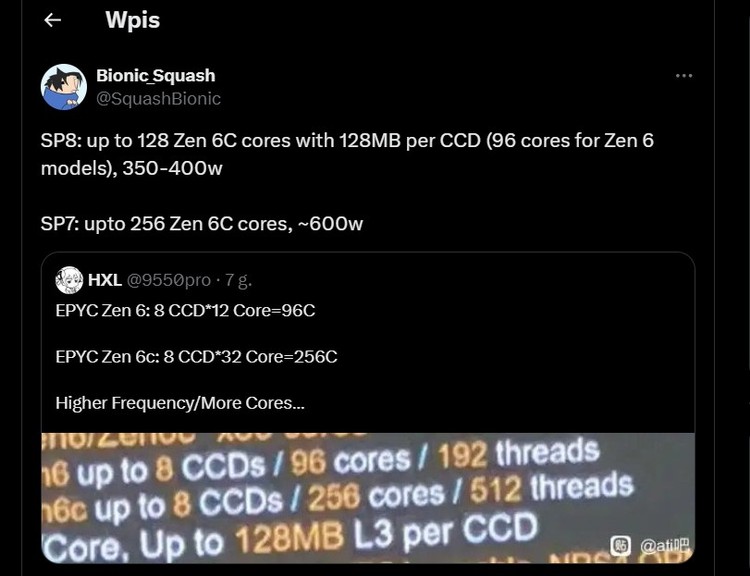

Przeciek potwierdza, że Venice przyjmie konfigurację do 8 CCD (Core Complex Die) z rdzeniami Zen6 lub Zen6c.

Procesor AMD EPYC 9006 Venice będzie wyposażony w maksymalnie 96 rdzeni Zen6 lub 256 rdzeni Zen6c i 128 MB pamięci podręcznej.

Procesor AMD EPYC 9006 Venice będzie wyposażony w maksymalnie 96 rdzeni Zen6 lub 256 rdzeni Zen6c i 128 MB pamięci podręcznej.

Przeciek potwierdza, że Venice przyjmie konfigurację do 8 CCD (Core Complex Die) z rdzeniami Zen6 lub Zen6c.

Co ważne, każdy CCD będzie zawierał do 12 rdzeni Zen6. Oznacza to, że następna konfiguracja EPYC będzie zawierała albo 96 rdzeni Zen6, albo 256 rdzeni Zen6c.

Ponadto potwierdza również, że każdy CCD będzie miał 128 MB pamięci podręcznej L3, co umożliwi łącznie 1 GB pamięci podręcznej L3.

Seria EPYC Venice prawdopodobnie będzie dostępna w dwóch wariantach, konkretnie dla gniazd SP7 i SP8.

Ten drugi ma być ograniczony do 128 rdzeni Zen6c lub 96 rdzeni Zen6 z TDP 350-400 W, podczas gdy SP7 będzie miał do 256 rdzeni i jeszcze wyższe TDP 600 W.

Wcześniej w tym tygodniu ten sam przeciekacz udostępnił schemat blokowy Venice. Nie jest to zdjęcie pełnej matrycy, tylko jej części, ale widoczna jest konfiguracja klasycznego projektu rdzenia z 12 rdzeniami na CCD.

Obecnie nie ma informacji na temat serii Ryzen 10. generacji, która również ma wykorzystywać 12-rdzeniowe układy CCD Zen6.

Jeśli jednak AMD planuje zachować gniazdo AM5 na kolejną generację, potwierdziłoby to obsługę do 24 rdzeni fizycznych w najwyższej konfiguracji.

Nie ma jeszcze żadnych komentarzy. Napisz komentarz jako pierwszy!